Recently a Chinese university has published a collection of slide-decks from various companies covering a server/HPC event. Among the slides, Intel had a seemingly longer comprehensive presentation describing Intel’s conceptual approaches to HPC to analysis of various workloads, and most interestingly, future plans and what looks to be an up-to-date server roadmap.

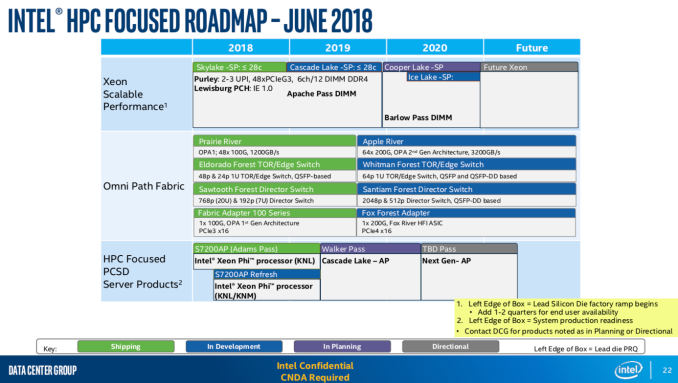

According to slides published by the Central South University from Changsha City, Hunan, Intel had to delay its Ice Lake-SP server platform from 2019 to 2020 because of the general delay of its 10 nm process technology. What was unknown and newly revealed in the roadmap, is that in addition to the codenamed Ice Lake-SP processors, the company is also preparing the codenamed Cooper Lake-SP CPUs that are set to arrive a bit ahead of the Ice Lake-SP chips. The document was demonstrated to students and professors by Intel itself at a special server/HPC event earlier this month.

Both Cooper Lake-SP and Ice Lake-SP processors will support the codenamed Barlow Pass DIMMs, which is most probably Intel’s next-generation Optane DC Persistent Memory DIMM running next-gen 3D XPoint non-volatile memory (though it is a speculation at this point). Intel does not disclose the difference between the Cooper Lake-SP and the Ice Lake-SP products, but it is possible that the former is the company’s “Plan B” for next-generation servers should anything happen with its 10 nm process technology or the ICL-SP design. Meanwhile, both Cooper Lake-SP and Ice Lake-SP will belong to one server platform that will also support an eight-channel per-socket memory sub-system along with multiple OmniPath fabric innovations.

Intel expects to begin production ramp of its Cooper Lake-SP CPUs in late 2019 or early 2020 with end user availability in late Q1 2020 or mid-2020. By contrast, the Ice Lake-SP will start their ramp sometimes in late Q1 2020 and will be available in Q3 or Q4 of 2020.

Another interesting thing to point out in Intel’s roadmap is that the company is prepping the codenamed Walker Pass platform and the codenamed Cascade Lake-AP processor for the HPC market segment. The aforementioned CPU is said to replace the Xeon Phi 7200-series “Knights Landing” processor for technical computing. Meanwhile, as the name suggests, the Cascade Lake-AP will heavily rely on Skylake SP-based design for mainstream servers.

Intel traditionally does not comment on information obtained unofficially and therefore we cannot find out how accurate the current roadmap is.

Related Reading:

- Power Stamp Alliance Exposes Ice Lake Xeon Details: LGA4189 and 8-Channel Memory

- Intel’s High-End Cascade Lake CPUs to Support 3.84 TB of Memory Per Socket

- Intel Documents Point to AVX-512 Support for Cannon Lake Consumer CPUs

- Intel Begins EOL Plan for Xeon Phi 7200-Series ‘Knights Landing’ Host Processors

- Intel Shows Xeon Scalable Gold 6138P with Integrated FPGA, Shipping to Vendors

- Sizing Up Servers: Intel's Skylake-SP Xeon versus AMD's EPYC 7000 - The Server CPU Battle of the Decade?

Via: Twitter / David Shor

from AnandTech https://ift.tt/2NHRX8g

via IFTTT

No comments:

Post a Comment