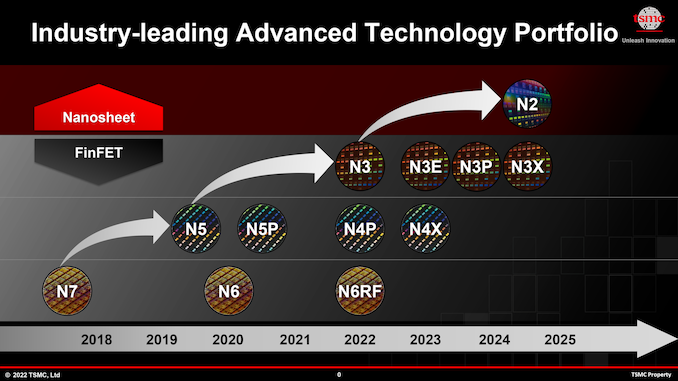

At its 2022 Technology Symposium, TSMC formally unveiled its N2 (2 nm class) fabrication technology, which is slated to go into production some time in 2025 and will be TSMC's first node to use their nanosheet-based gate-all-around field-effect transistors (GAAFETs). The new node will enable chip designers to significantly reduce the power consumption of their products, but the speed and transistor density improvements seem considerably less tangible.

TSMC's N2 is a brand-new platform that extensively uses EUV lithography and introduces GAAFETs (which TSMC calls nanosheet transistors) as well as backside power delivery. The new gate-all-around transistor structure promises well-published advantages, such as greatly reduced leakage current (now that the gates are around all four sides of the channel) as well as ability to adjust channel width to increase performance or lower power consumption. As for the backside power rail, it is generally designed to enable better power delivery to transistors, offering a solution to the problem of increasing resistances in the back-end-of-line (BEOL). The new power delivery is slated to increase transistor performance and lower power consumption.

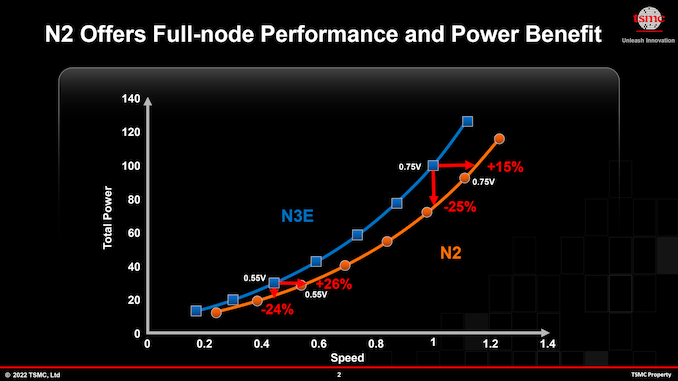

From feature set standpoint, TSMC's N2 looks like a very promising technology. As for actual numbers, TSMC promises that N2 will allow chip designers to increase performance by 10% to 15% at the same power and transistor count, or reduce power consumption at the same frequency and complexity by 25% ~ 30%, all the while increasing chip density by over 1.1-fold when compared to N3E node.

| Advertised PPA Improvements of New Process Technologies Data announced during conference calls, events, press briefings and press releases |

|||||

| TSMC | |||||

| N5 vs N7 |

N3 vs N5 |

N3E vs N5 |

N2 vs N3E |

||

| Power | -30% | -25-30% | -34% | -25-30% | |

| Performance | +15% | +10-15% | +18% | +10-15% | |

| Chip Density* | ? | ? | ~1.3X | >1.1X | |

| Volume Manufacturing |

Q2 2022 | H2 2022 | Q2/Q3 2023 | H2 2025 | |

*Chip density published by TSMC reflects 'mixed' chip density consisting of 50% logic, 30% SRAM, and 20% analog.

Versus N3E, the performance improvements and power reductions enabled by TSMC's N2 node are in line with what the foundry's new nodes typically bring in. But the so-called chip density improvements (which should reflect transistor density gains) are just a little over 10%, which is not particularly inspiring, especially considering that N3E already offers a slightly lower transistor density when compared to vanilla N3. Keeping in mind that SRAM and analog circuits barely scale these days, mediocre improvements in transistor density of actual chips should probably be expected these days. However, a chip density improvement of 10% in about three years is certainly not great news for GPUs and other chips that live or die based on rapidly increasing their transistor counts.

Bearing in mind that by the time TSMC's N2 enters production the company will also have the density-optimized N3S node, it would appear that the foundry will have two process technologies based on different types of transistors yet offering very similar transistor densities, something that has never happened before.

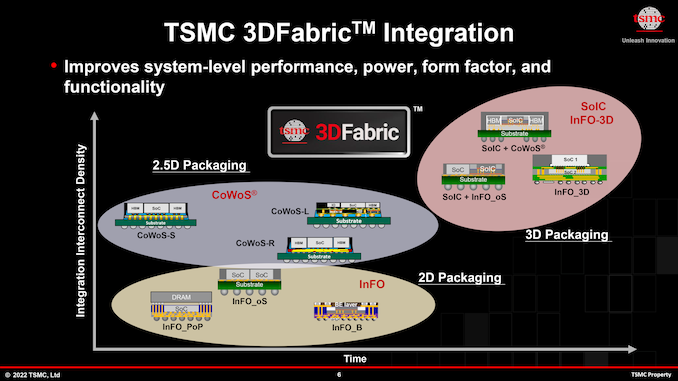

As usual, TSMC will offer their N2 node with various features and knobs to allow chip designers to optimize for things like mobile and high-performance computing designs (note that TSMC calls HPC everything that is not mobile, automotive or specialty. which includes everything from a low-power laptop CPU to a high-end compute GPU aimed at supercomputers). Also, platform offerings include something that TSMC calls 'chiplet integration', which probably means that TSMC enable its customers to easily integrate N2 chips into multi-chiplet packages made using various nodes. Since transistor density scaling is slowing down and new process technologies are getting more expensive to use, multi-chiplet packages are going to become more common in the coming years as developers will be using them to optimize their designs and costs.

TSMC expects to start risk production of chips using its N2 fabrication process sometimes in the second half of 2024, which means that the technology should be available for high volume manufacturing (HVM) of commercial products in the second half of 2025. But, considering the length of modern semiconductor production cycles, it's likely more pragmatic to expect the first N2 chips to become available either very late in 2025 or 2026, if everything goes as planned.

from AnandTech https://ift.tt/RZOkb6m

via IFTTT

No comments:

Post a Comment