One of the world's biggest semiconductors and manufacturers of DRAM, SK hynix, has unveiled it has working samples of a new generation of memory modules designed for HPC and servers. Dubbed Multiplexer Combined Ranks (MCR) DIMMs, the technology allows high-end server DIMMs to operate at a minimum data rate of 8 Gbps, which is an 80% uptick in bandwidth compared to existing DDR5 memory products (4.8 Gbps).

Typically, the most common way to ensure higher throughput performance on DIMMs is through ever increasing memory bus (and chip) clockspeeds. This strategy is not without its drawbacks, however, and aiming to find a more comprehensive way of doing this, SK hynix, in collaboration with both Intel and Renesas, has created the Multiplexer Combined Rank DDR5 DIMM.

Combining Intel's previously-unannounced MCR technology for its server chips and Renesas's expertise in buffer technology, SK hynix claims that their DDR5 MCR DIMM has 66% more bandwidth than conventional DDR5 DIMMs, with an impressive 8 Gbps/pin (DDR5-8000) of bandwidth. SK hynix themselves claim that the MCR DIMM will be 'at least' 80% faster than what's currently out there DDR5-wise, but it doesn't quantitate how it reaches this figure.

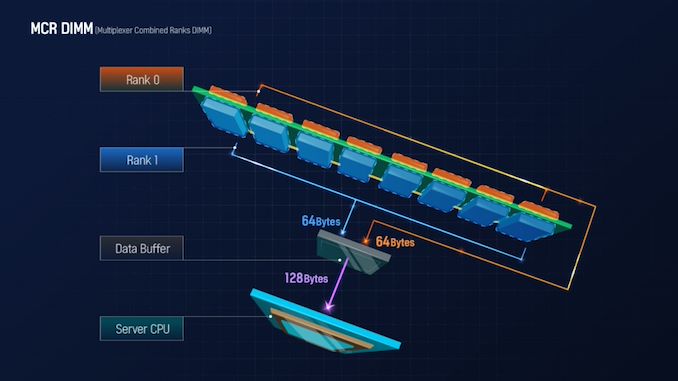

The technology behind the MCR DIMM is interesting, as it enables simultaneous usage of two ranks instead of one, in essence ganging up two sets/ranks of memory chips in order to double the effective bandwidth. Unfortunately, the details beyond this are slim and unclear – in particular, SK hynix claims that MCR "allows transmission of 128 bytes of data to CPU at once", but looking at the supplied DIMM photo, there doesn't seem to be nearly enough pins to support a physically wider memory bus.

More likely, SK hynix and Intel are serializing the memory operations for both ranks of memory inside a single DDR5 channel, allowing the two ranks to achieve a cumulative effective bandwidth of 8Gbps. This is supported by the use of the Renesas data buffer chip, which is shown to be on the DIMM in SK hynix's photos. Conceptually, this isn't too far removed from Load Reduced DIMMs (LRDIMMs), which employs a data buffer between the CPU and memory chips as well, though just how far is difficult to determine.

More curious, perhaps, is that this design puts a great deal of faith into the ability of the physical memory bus and host controller (CPU) to be able to operate at DDR5-8000 (and higher) speeds. Normally the bottleneck in getting more memory bandwidth in server-grade systems is the memory bus to begin with – having to operate at slower speeds to accommodate more memory – so going a route that requires such a fast memory bus is definitely a different approach. In either case, the ability to run DIMMs at DDR5-8000 speeds in a server would be a significant boon to memory bandwidth and throughput, as that's often in short supply with today's many-core chips.

As SK Hynix has partnered up with Intel via its MCR technology and using buffer technology from Renesas, MCR would seem to be an Intel-exclusive technology, at least to start with. As part of SK hynix's press release, Intel for its part stated that they "look forward to bringing this technology to future Intel Xeon processors and supporting standardization and multigenerational development efforts across the industry.” In the interim, this appears to be a technology still under active development, and SK hynix is not publishing anything about availability, compatibility, or pricing.

While SK Hynix hasn't gone too much into how MCR DIMM is twice as fast as conventional DDR5 memory, this product is designed for the high-performance computing (HPC) and server industries, and it's unlikely we'll see MCR DIMMs in any form on consumer-based systems. We expect to learn more in the not-too-distant future.

Source: SK Hynix

from AnandTech https://ift.tt/I8ReurE

via IFTTT

No comments:

Post a Comment