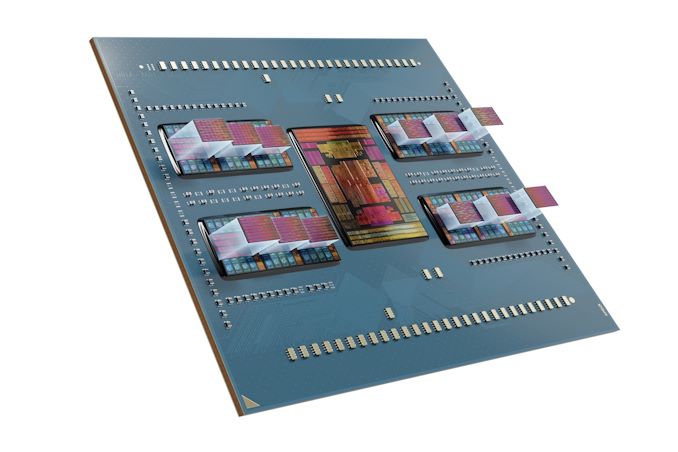

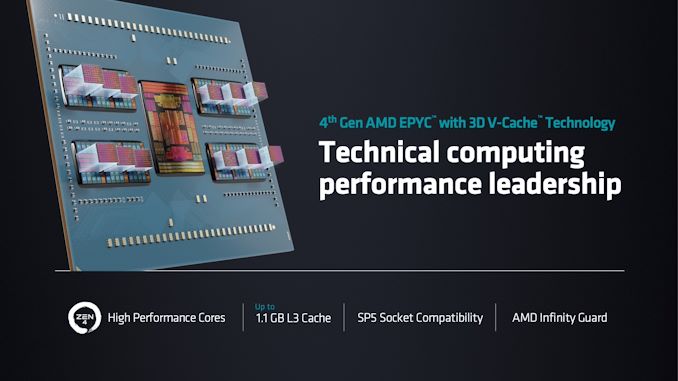

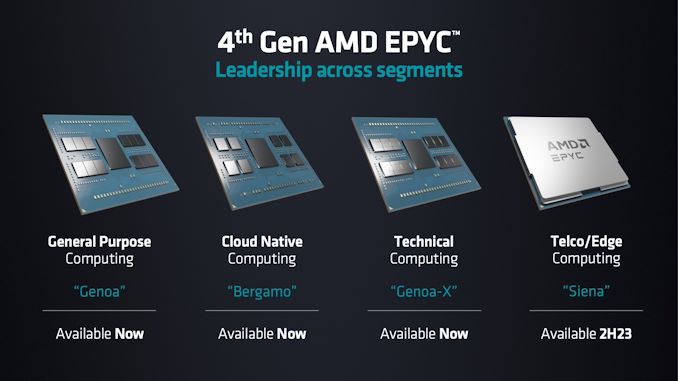

Alongside today’s EPYC 97x4 “Bergamo” announcement, AMD’s other big CPU announcement of the morning is that their large cache capacity “Genoa-X” EPYC processors are shipping now. First revealed by AMD back in June of last year, Genoa-X is AMD’s now obligatory V-cache equipped EPYC server CPU, augmenting the L3 cache capacity of AMD’s core complex dies by stacking a 64MB L3 V-cache die on top of each CCD. With this additional cache, a fully-equipped Genoa-X CPU can offer up to 1152MB of total L3 cache.

Genoa-X is the successor to AMD’s first-generation V-cache part, Milan-X. Like its predecessor, AMD is using cache die stacking to add further L3 cache to otherwise regular Genoa Zen 4 CCDs, giving AMD a novel way to produce a high-cache chip design without having to actually lay out an fab a complete separate die. In this case, with 12 CCDs on a Genoa/Genoa-X chip, this allows AMD to add 768MB of additional L3 cache to the chip.

Like its predecessor, these high-cache SKUs are aimed at a niche market segment of workloads that benefit specifically from the additional cache, which AMD terms their “technical computing” market. To make full use of the additional cache, a workload needs to be cache capacity limited – that is to say, it needs to significantly benefit from having more data available on-chip via the larger L3 cache. This typically only a subset of server/workstation workloads, such as fluid dynamics, databases, and electronic design automation, which is why these high cache chips serve a narrower portion of the market. But, as we saw with Milan-X, in the right situation the performance benefits can be significant.

As these are otherwise stock Genoa chips, Genoa-X chips use the same SP5 socket as Genoa and Bergamo. AMD hasn’t disclosed the TDPs, but based on Milan-X, we’re expecting a similar range of TDPs. The additional cache and its placement on top of the CCD means that V-cache equipped CCDs are a bit more power hungry, and the cache die does pose some additional challenges with regards to cooling. So there are some trade-offs involved in performance gains from the extra cache versus performance losses from staying within the SP5 platform’s TDP ranges.

As with Bergamo, we expect to have a bit more on Genoa-X soon. So stay tuned!

from AnandTech https://ift.tt/rBkmFHX

via IFTTT

No comments:

Post a Comment