Intel this week became a member of CHIPS Alliance, an industry consortium that is working to accelerate the development of open source SoCs (and SiPs) for various applications. As part of their membership, Intel has also contributed its Advanced Interface Bus to the group, giving developers access to the bus and thus the means to interoperate with Intel (and other) chips that will be using it.

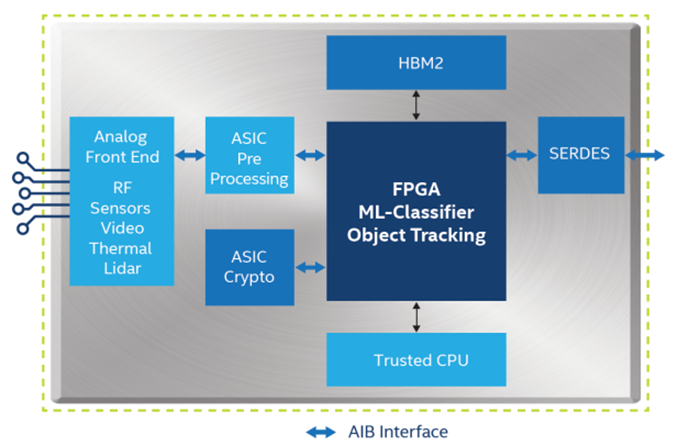

Designed for use with system-in-packages (SiPs) devices, Intel’s AIB is a high-bandwidth, low-power, die-to-die PHY level standard that uses a clock forwarded parallel data transfer mechanism (akin that used by modern DDR DRAM interfaces). The technology is agnostic to manufacturing processes and packaging technology, so it can be used to connect a wide variety of chips/chiplets using different types of packages, including Intel’s own EMIB, TSMC’s CoWoS, or other 2.5D technologies from numerous vendors.

Intel’s AIB has been available to third parties on a royalty-free basis for a while now, so contributing the technology to CHIPS Alliance is the next step for Intel in increasing its adoption. By making AIB available to a very broad group of chip designers, Intel is encouraging development of an ecosystem of chiplets that can later be used with its own CPUs, GPUs, FPGAs, and other components to build special-purpose multi-die SiPs.

Now that CHIPS Alliance controls Advanced Interface Bus specification, further development of the technology will be handled by its Interconnects workgroup, which is set to begin its operations shortly. As a part of the consortium, Intel will be able to further contribute to development of AIB. Meanwhile, Intel will get a seat on the governing board of CHIPS Alliance.

Dr. Zvonimir Bandić, Chairman, CHIPS Alliance, and senior director of next-generation platforms architecture at Western Digital said the following:

“Intel’s selection of CHIPS Alliance for the AIB specifications affirms the leading role that the organization impacts for open source hardware and software development tools. We look forward to faster adoption of AIB as an open source chiplet interface.”

Related Reading:

- Intel Provides Royalty-Free License for Data Bus to DARPA’s Modular Chips Initiative

- An Interconnected Interview with Intel’s Ramune Nagisetty: A Future with Foveros

- Intel’s Xe for HPC: Ponte Vecchio with Chiplets, EMIB, and Foveros on 7nm, Coming 2021

- Intel’s EMIB Now Between Two High TDP Die: The New Stratix 10 GX 10M FPGA

- Arm Joins CXL Consortium

- AMD Joins CXL Consortium: Playing in All The Interconnects

- Compute Express Link (CXL): From Nine Members to Thirty Three

- CXL Specification 1.0 Released: New Industry High-Speed Interconnect From Intel

- Gen-Z Interconnect Core Specification 1.0 Published

Source: CHIPS Alliance

from AnandTech https://ift.tt/2sTvnVs

via IFTTT

No comments:

Post a Comment