At the annual RISC-V Summit this week, Samsung disclosed the use SiFive’s RISC-V cores for upcoming chips for a variety of applications. The company is joining a growing list of leading high-tech companies that have adopted the RISC-V architecture.

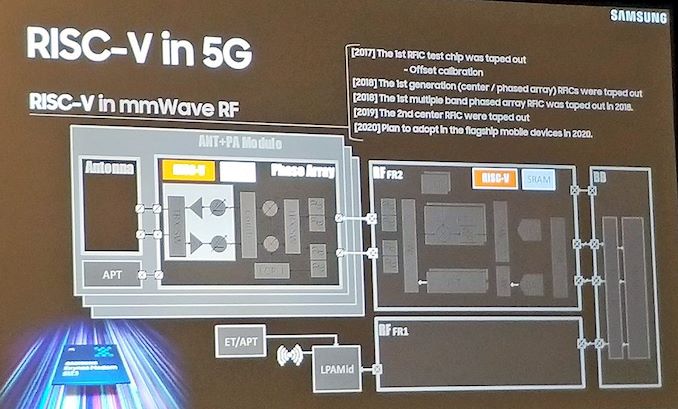

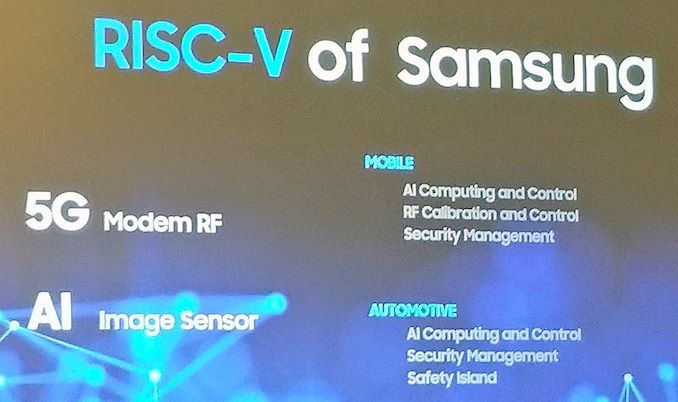

One of the applications that Samsung is using RISC-V cores in is mmWave RF processing by its upcoming 5G RF front-end modules. The latter will be used for Samsung’s flagship 5G smartphones due in 2020. The RISC-V cores will also be used for AI image sensors, security management, AI computing & control.

It is noteworthy that Samsung taped out its first chip with a RISC-V core(s) as early as in 2017, so it started to work on it even earlier. In three years, Samsung has iterated on its designs and is now planning to adopt RISC-V cores for commercial applications, starting from mmWave RF processing in mobiles and expanding beyond them.

Besides the announcement of the RISC-V core integration, it's also Samsung's first instance of them talking about their mmWave modules in public. Unlike Qualcomm, Samsung tends to remain quiet about their developments until it's nearing commercialisation, and even then in a lot of cases we don't know too much about their designs. Nevertheless, it looks like the company has had mmWave designs for some time.

Samsung will be the fourth major company that has publicly disclosed its plans to adopt the open-source RISC-V architecture after Western Digital, NVIDIA, and Qualcomm. Western Digital intends to use the technology for a variety of applications, including SSD and HDD controllers. NVIDIA reportedly plans to use it for GPU memory controllers, whereas Qualcomm is set to use RISC-V for mobile SoCs.

All of the said companies have historically used processing cores based on architectures developed by Arm, and will likely continue to use them in the foreseeable future alongside RISC-V implementations. The advantage of RISC-V and the rationale for the vendors like Samsung choosing SiFive designs over Arm designs might be financial, as the former is likely undercutting its big competitor in price. For vendors doing their own microarchitecture designs, such as WD, RISC-V comes with no royalties attached, and offered more flexibility for vendors in terms of implementation. Arm only recently changed course in allowing vendor to implement their own custom instructions to the Cortex designs and architecture. Custom instructions developed by SoC vendors might be a huge benefit for efficient handling of ECC and RF processing among other things.

Related Reading:

- SiFive Announces First RISC-V OoO CPU Core: The U8-Series Processor IP

- Western Digital’s RISC-V "SweRV" Core Design Released For Free

- Western Digital Reveals SweRV RISC-V Core, Cache Coherency over Ethernet Initiative

- Western Digital to Use RISC-V for Controllers, Processors, Purpose-Built Platforms

Sources: The Register, Chris Williams/Twitter

from AnandTech https://ift.tt/35hyOTI

via IFTTT

No comments:

Post a Comment